Skrivet av mpat:

Intel är inte speciellt rädda för att jobba, dock. Det absolut lättaste hade ju varit att inte göra något alls.

Jo, jag vet att det är samma opkoder som innan, men jag tänker på AMDs trick från Zen, där de accepterar instruktioner med längre vektorer än vad de egentligen har enheter för, och exekverar dem över flera cykler. Intel hade ju kunnat göra så, så hade binärerna fungerat på alla processorer…om det är det man vill. Det kanske är där skon klämmer, att de vill sälja Xeon-processorer med stöd för de längre vektorerna för multum.

Prioritet

Ett av de kritiska designkriterierna för APX (och därmed AVX10) är att det ska gå att implementera med en relativt liten transistorbudget. Uppenbara sättet att göra något sådant är att behålla så mycket som möjligt så nära vad som redan finns.

Å ena sidan kan man se det som "glaset halvtomt", det finns helt klart nackdelar. x86 är redan rejält komplex att avkoda, detta gör det ännu lite värre.

En annan är att det i praktiken helt raderar ut en av fördelarna med "CISC": kompakta instruktioner. Kortast möjliga instruktion med REX2 blir 3 byte, de flesta kommer vara 4 byte eller längre. AVX10 (EVEX-prefix) instruktioner verkar vara minst 6 byte(!) långa.

Å andra sidan kan man se det som "glaset halvfullt", stora fördelen är att det går att införa gradvis då man är helt bakåtkompatibel. Vidare verkar Intel använda en ABI som gör att "gammal" kod kommer kunna anropa in i bibliotek som använder APX-finesser, det på ett sätt som inte kräver någon förändring av anropen (applikationen).

Som @Findecanor skriver är AVX10 (nästan) exakt samma sak som AVX-512 + tillägg av statusregister som egentligen säger: jag stödjer all AVX-512 instruktioner, fast bara med 128-bit och 256-bit register.

"Dubbelpumpad" SIMD

Min gissning varför man inte tog samma väg som AMD gjort i Zen4 är dessa:

1. register är i praktiken en form av cache, en cache vars utformning gör att det tar massor med transistorer. Finns en uppskattning att de 32 AVX-512 registren tar 6-7 % av kretsytan av "compute-kretsen" i Zen4. Det väldigt mycket redan i en P-core, det blir orimligt mycket i en E-core (där andelen skulle vara signifikant högre då dessa är flera gånger mindre än en P-core).

2. det är inte 100 % AVX-512 instruktioner med endast 128-bit och 256-bit resultat, AVX10 skiljer sig i vissa lägen för att få in stödet för ökning från 16 till 32 heltalsregister.

3. om det inte finns 512-bit register behöver man inte heller spara/återställa dessa vid kontext-switch. 32 st 512-bit register tar 2k, det är ~94 % av alla register som måste sparas vid en kontext-switch (minskar till 89 % när man ökar från 16 till 32 heltalsregister). Med 256-bit register utgör de "bara" 80 % (även de 8 mask-register i AVX-512 kan då minskas till halva storleken).

4. finns egentligen ingen vinst med bredare register än vad man har data-path till, utöver kompatibilitet. I teorin finns en vinst då det blir färre instruktioner, men det SIMD typiskt är bra på tenderar ha data-throughput som flaskhals och inte instruktions-throughput (ofta logiskt rätt enkel kod).

Om dessa gissningar är någorlunda rätt blir nästa gissning att 1. och 2. har ganska mycket högre prio jämfört med de två sista.

SVE-like

Något likt SVE skulle i praktiken betyda en helt ny instruktionsuppsättning, samtidigt som man inte kan ta bort SSE/AVX utan att paja kompatibiliteten. Arm tog en väldigt stor risk när de designade en ny ISA från scratch med ARM64, de flesta tidigare sådana försök har misslyckats rätt kapitalt... De måste helt enkelt förutsatt att det inom relativt kort tid skulle gå att droppa 32-bit ISA:an. Tog Apple ett par år (A6/A6X var sista CPU med stödet), tog Arm 10-12 år (ARM64 ISA släptes 2010, första Arm CPU med ARM64 stöd släpptes 2012), båda får anses vara i sammanhanget väldigt snabbt.

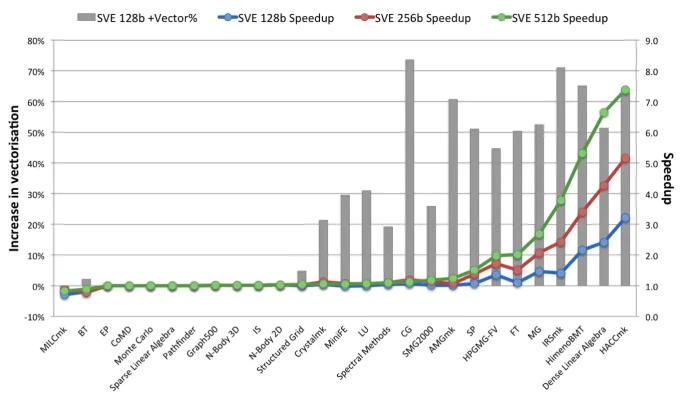

På mobil/desktop ARM64 har alla så här långt nöjt sig med 128-bit fysiska register (är bara Fujitsu A64FX som kör något större, den har 512-bit). Det är mer flexibelt med 4 st 128-bit pipelines (vilket är vad både Apple Silicon och nu även Cortex X2/X3 kör med) jämfört med 2 st 256-bit pipelines: båda ger samma peak-kapacitet, fördelen förra är att man enklare når nära peak, fördelen med den senare är att det tar färre transistorer.

Och Apple har inte ens brytt sig om att implementera SVE än, men precis som för AVX-512 även med 128-bit instruktioner finns fördelar med SVE över NEON (som är Arms motsvarighet till SSE, eller mer likt AVX med 128-bit register).