Intels sista korrekta siffra är 32nm, dvs Sandy Bridge. 22nm är tät som en 26nm ungefär, men ändå en massiv förbättring eftersom det var första FinFET. Detta gjorde att alla andra tillverkare släppte alla hämningar i namngivningen - innan dess småfuskade de, men nu ligger de allihop minst en nod fel. Intel försökte istället ”komma ikapp” med de gamla numren, så deras 14nm är tät som en 16nm, och med 10nm skulle de vara tillbaka på plan. TSMC gick från 20nm till ”16” utan att krympa alls (man lade bara till FinFET), gjorde en ”10nm” som var ungefär som Intels ”14nm” och sedan en ”7nm” som var tät som Intels 10nm. Vad 5nm skall jämföras med vet jag inte, för det finns ingen annan som kommit så långt än, men det är knappast en dubbelkrympning.

Jag hänger inte riktigt med, du pratar om täthet, med det låter även som att du använder gate length som måttstock? Som mycket riktigt gick mer hand i hand med nodnamnet fram till runt 32nm, sen har den ju vart märkligt använd även åt andra hållet T ex TSMC 28nm hade en gate length på 24nm. Men tätheten står ju inte och hänger på enbart den detaljen, utan det finns många andra tekniker (finfet som du nämner t ex) och komponenter man kan krympa för att nå högre densitet, vilket i slutändan är det centrala ändå, gate length är ju egentligen lite skitsamma.

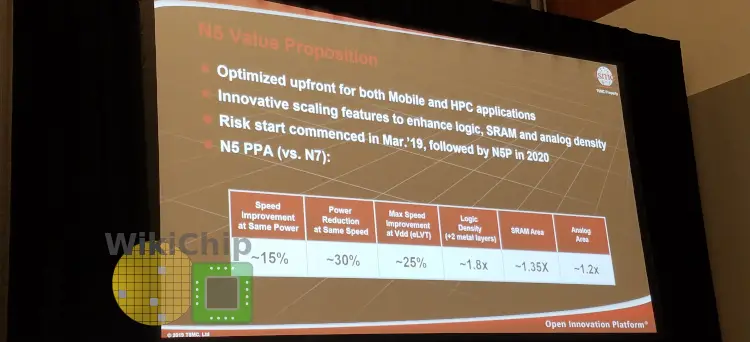

Kollar man på tätheten hos TSMC noder, ser det ut som att varje helnod (inte + noder) har ökat densitet med ca 1.8X från föregående. Ryktas ju om att TSMC 5nm faktiskt har en MTr/mm2 runt 170, vilket är rejält mycket tätare än någon annan nod i produktion (värt att notera att faktsika kretsdesigner inte designas så tätt dock).